数字电子技术

知识储备

二进制编码

数字信号是离散信号的数字化表示,其变化量是最小量的整数倍,表示方法是二值逻辑/二进制。计算机使用二进制表示信息,这些二进制数就是所谓的代码,给每一组代码赋予一定的含义就是编码。编码有有权码和无权码之分,常见的有权码有 8421 码、5421 码、2421 码等,无权码有余三码、余三循环码、格雷码等。二进制在物理实现上用高低电平两种状态进行表示,电信号的状态易于区分、抗干扰能力较强。二值逻辑在实现上需要对逻辑电平的标准有统一的规定,即高电平和低电平的电压范围,常用的标准有 TTL、CMOS、RS232。不同标准对高低电平的定义不尽相同,使用不同逻辑电平标准的器件时,就需要电平转换芯片充当翻译的角色,使信息能够被准确传递。

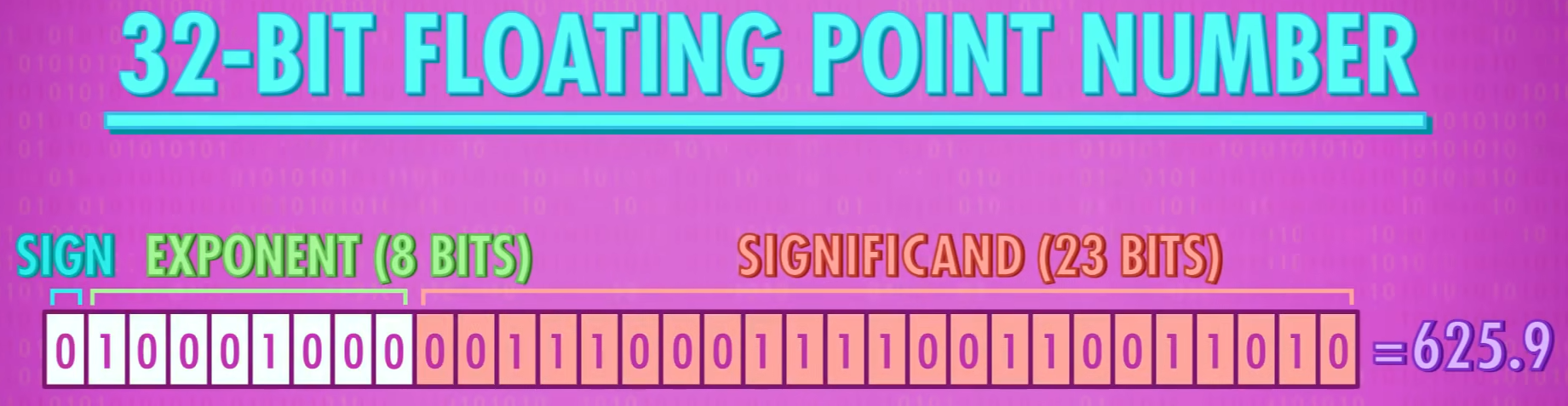

相较于十进制,二进制在表示同样的数时需要更多的位数,用加权的方式,可以在不同数制之间互相转化。二进制只是一种十进制以外的数制,其运算规则与十进制无异。一个数叫一位,8 位叫一个字节;二进制中,1kb 为 1024 byte。大部分计算机用第一位表示正负,剩下位数表示数字。小数在计算机中被称为浮点数,因为小数点可以在数字间浮动。浮点数的表示类似于科学计数法。文字按照一定的编码方式对应为一串二进制数,因此也可由几位二进制数表示。ASCII 用 7 位二进制数表示字母,数字,标符号和特殊命令符号。而对于中文和日文这样有成千上万个字符的语言,各国有不同的多字节编码方案,但互不兼容。为此诞生了 Unicode,统一了所有的编码标准,最常见的 Unicode 是 16 位的。音频是时间上的一维信号,图片/颜色是二维的矩阵或者张量信号,视频则是由一帧帧图片构成,这些信息均可以由二进制编码。在机器中使用的连同符号一起数码化的二进制数称为机器数,机器数对应的真正数值称为真值。8 位机器数表示的真值范围为 0-255,16 位真值表示的真值范围为 0-65535。

## 布尔代数及实现

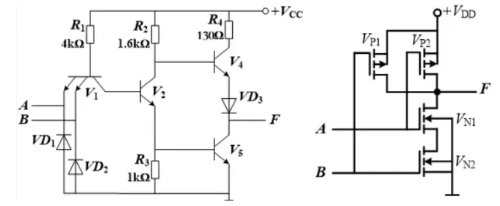

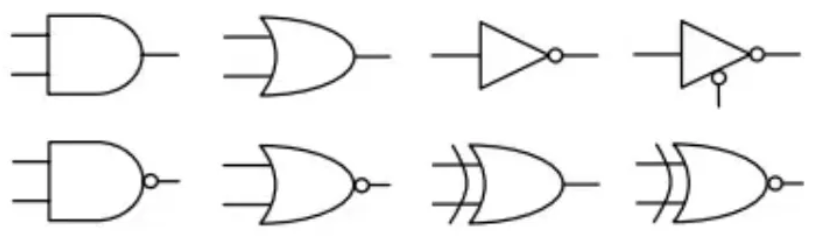

布尔代数是专门研究二值逻辑的数学结构,真值表是其中的重要工具,用于列举逻辑表达式(逻辑函数)在所有可能输入情况下的结果。在设计逻辑电路的过程中,需要对逻辑函数进行化简,可以使用公式、卡诺图、QM 法等方法完成操作,常见公式和方法具体步骤的资料丰富,此处省略。布尔代数定义了与、或、非、与非、或非、异或、同或七种基本运算。基本运算叠加复合,可以构成许多实用的逻辑函数。有了逻辑函数的概念后,还需要用电路去实现,以 TTL 和 CMOS 与非门为例,内部结构分别如下

利用二极管、三极管、场效应管等晶体管,可以构成全部七种能完成基本运算的逻辑门,实际使用时都是封装好的成熟芯片,故一般无需掌握其内部结构,但对芯片数据手册中的常用参数(阈值电压、噪声容限、扇出系数、传输延迟时间、动态尖峰电流等)需要了解含义,以便选型。除了七种基本逻辑运算,OC/OD 门和三态门也是常用的两种逻辑门,OC/OD 门的逻辑功能和普通逻辑门相同,但内部结构有所不同,用于配合上拉电阻用于实现线与的逻辑(线与多根信号线连在一起,一根信号线输出低电平则整个输出低电平),其电路符号和普通逻辑门相同。三态门用于实现信号的分时复用,三态即除了高低电平外还有高阻态,高阻态是一种特殊的 “断开” 状态,此时接口在电气上与外部电路几乎隔离,不影响其他电路的工作,通常用于避免总线上的数据冲突

组合逻辑电路

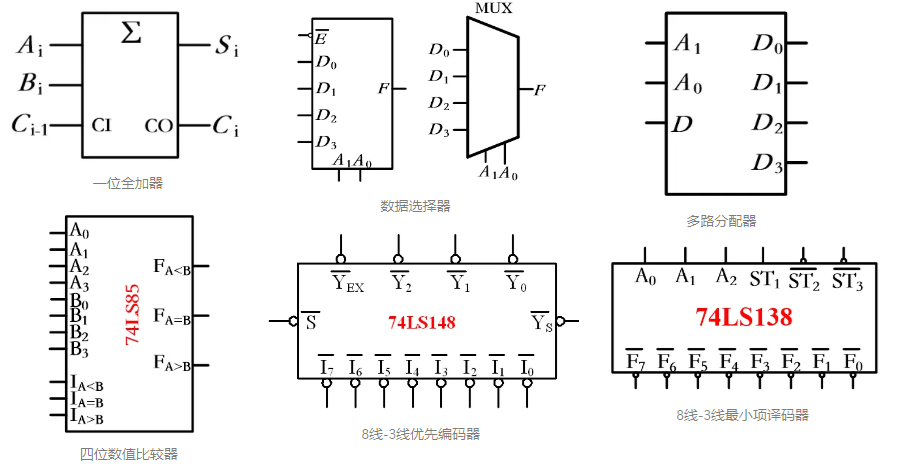

组合逻辑电路由逻辑门构成,无反馈环节或记忆能力。设计组合逻辑电路的思路为:确定输入输出,列出真值表,化简逻辑函数,用逻辑门实现。常用的逻辑功能已被封装为成熟的芯片,可直接使用这些组件进行更高层次的设计,比如级联或构成功能丰富的系统。同理也无需掌握这些芯片的内部结构,充分理解功能特点以及必要的选型参数参数即可。常用的逻辑电路模块举例如下,对于一般的逻辑电路芯片,查阅芯片手册可以了解到详细信息。

- 全加器:一位二进制数的加法,考虑进位;可级联成多位的加法器;配合补码的概念也可实现减法

- 数据选择器:在多个输入信号中选择一个传输到输出;可级联扩大选择范围

- 多路分配器:将一个输入信号选择传输到多个输出中的一个;可级联扩大选择范围

- 数值比较器:比较两个相同位数的二进制数的大小,可用于标志位的产生;可级联增加比较的位数

- 编码器:将一组二进制代码赋予特定的含义(如表示为对应的十进制数);可级联增加支持的线数

- 译码器:输入二进制代码,输出还原之后的特定输出信号;可级联增加支持的线数;将输出信号接到发光二极管上,就是所谓的显示译码器;当每个输出都是输入变量的最小项时,又称为最小项译码器。最小项译码器可以实现当前输入个数下的任意逻辑函数

时序逻辑电路

时序逻辑电路由逻辑门和存储器构成,有反馈环节和记忆能力。时序逻辑电路接收信号之前的状态称为初态/原态,用$Q^n$表示,接收信号之后建立的新稳态称为次态/新态,用$Q^{n+1}$表示。所谓有记忆能力,就是指次态同时由输入和初态决定。相较于组合逻辑电路的输入而言,时序逻辑电路更重要的往往是时钟信号/触发信号的输入。复杂系统中,往往用时钟信号/触发信号来保证各个信号的动作在时间上同步。时序逻辑电路的表示方式有时钟方程+驱动方程+输出方程+状态方程,状态转换图,次态卡诺图等。

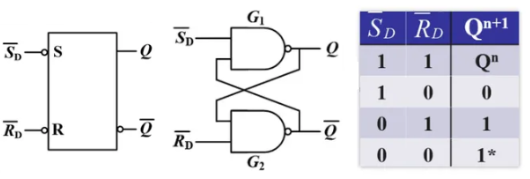

存储器的基本单元是触发器(Flip-Flop,简称 FF),基本 RS 触发器也叫锁存器(latch),其基本结构和真值表如下,通过改变输入信号,可以实现对状态 Q 的存储、置位和复位。这样的触发器可以存储一位的信息,将它们并排使用便可以存储更多位数的信息,比如存储八位信息的寄存器、移位寄存器等更复杂的存储结构。

触发器按逻辑函数实现的功能又细分为 RS 触发器、JK 触发器、D 触发器、T 触发器、T'触发器;按结构又细分为基本型触发器、同步型触发器、主从型触发器、边沿型触发器。触发器有电平触发和边沿触发,狭义上的触发器指边沿触发,而电平触发的叫锁存器。寄存器的基本组成单元为触发器/锁存器。而缓冲器与三者不同,没有数据保存的功能而更像是一个开关,主要用于隔离和增强信号的驱动能力。

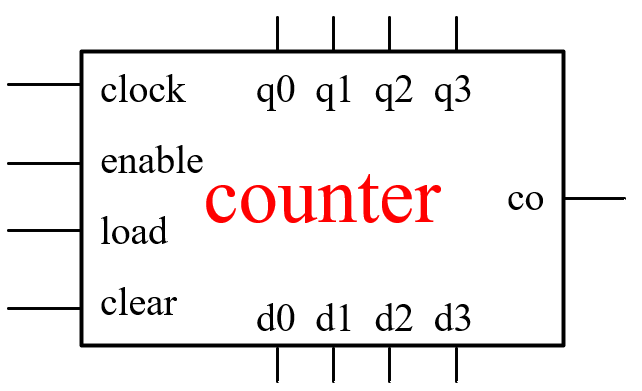

时钟信号是时序逻辑电路中的重要概念,常用于计数、分频、定时、产生脉冲序列等。使用专门的振荡器或晶振产生固定频率的方波信号,对这种方波信号计数,就可以实现较为精确的计时,进一步可以结合传感器完成测速等一系列应用。计数这个操作由计数器这种电路结构实现,计数器由触发器和逻辑门构成。触发器之间采用不同的连接方式,可以跳过某些计数值从而实现任意进制的计数器、环形计数器、扭环形计数器、提供自启动功能等。

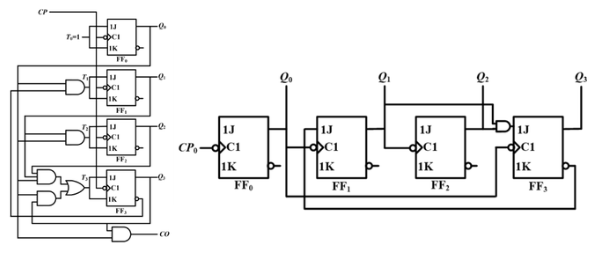

计数器分为同步计数器和异步计数器,同步计数器所有位的触发器均受时钟信号约束,工作频率高、传输延迟短、结构复杂;而异步计数器低位输出直接控制高位输入,结构简单,存在竞争和冒险产生的尖峰脉冲。下图左侧为同步计数器结构,右侧为异步计数器结构。