FPGA理论知识(1)

Xilinx FPGA硬件结构

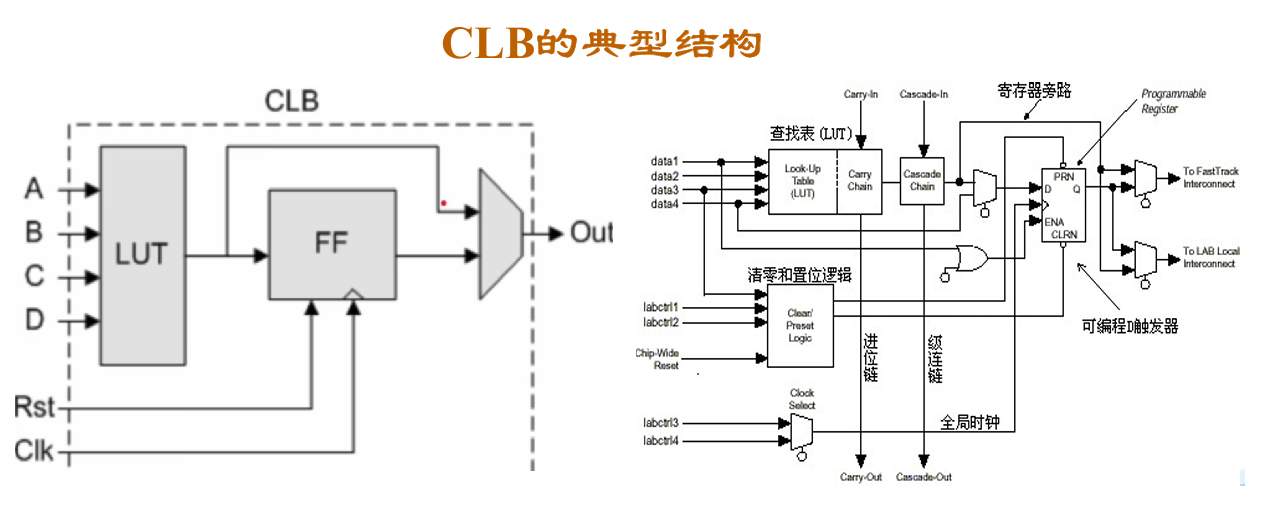

基本单元

Xilinx FPGA 以可配置逻辑块 CLB 为基本逻辑资源单元。每个 CLB 中包含若干 Slices。最基本的 Slice 包含查找表 LUT 和触发器 Flip-Flop 资源。LUT 是存储真值表的介质,也可用作分布式 RAM 作为快速高效的 on-chip memory。LUT 由 MUX 树和 SRAM 构成,工作时由输入信号控制 MUX 树,从 SRAM 配置位中选中一个值输出。以四输入的 LUT 为例,使用 15 个 MUX2 分为四层(8-4-2-1)来实现十六选一的结构,SRAM 中存储 16 个位对应应该存储的二进制值即可。

今天的 Xilinx FPGA 中,除了上述基本单元之外,还集成了 IO Blocks(输入输出物理接口)、嵌入式 Block RAM(存储资源)、PLL(高速时钟信号)、Global Clock Buffers(时钟布线资源)、DSP Blocks(数字信号处理)、SERDES(高速接口)、CPU(硬核处理器)、NPU(硬核 AI 推理)以及配套的多路选择器 Mux、进位链 Carry Chain、局部互联资源等。集成这些硬核单元设计出这样的架构,是基于解决实际问题和成本效率综合考量后,高度优化的结果。

存储资源

存储资源分为 Distributed RAM 和 Block RAM,前者使用 CLB 资源,后者是器件上专用的块状存储资源。高端的芯片除了这种中 RAM 之外,还会配备 Ultra RAM 资源。Ultra RAM 是大容量、省 LUT 的片上 RAM,数量少且延迟略高,适合作大缓存使用。

Block RAM(BRAM)是 FPGA 中固化的硬件存储单元,固定容量为 18K bits(18432 bits),可以单独使用也可以两个相邻的 18k BRAM 组合成双口 36k BRAM。设计中调用的资源以 BRAM 为最小单位,向上取整。例如存储位宽为 16 位,数据深度为 512,总共占用 16*512 = 8192 bits = 1KBytes。数据宽度指一个数据占用的 bit 位数,数据深度指可以存放的数据个数。数据深度与地址线宽度有关,如数据深度为 512,则对应的地址线为 9 位,\(2^9=512\)。

这些物理存储结构被抽象为逻辑存储结构,最常用的是 RAM、ROM 和 FIFO。RAM 和 ROM 中任意一个存储单元都可以在相同时间内被访问,硬件上由存储单元阵列 + 地址译码器 + 读写电路构成;ROM 由 RAM 配合要预先写入的 coe 文件实现。FIFO 是先进先出队列存储器,内部常用环形缓冲区的结构,由 RAM+读写指针实现。根据读写时钟,可以分为同步 FIFO 和异步 FIFO,同步 FIFO 的读写时钟相同,异步 FIFO 的读写时钟不同。

这些逻辑存储结构的实现原理了解即可,Xilinx 对它们均提供了成熟的 IP 供开发者使用。RAM 和 ROM 的 IP 有 Distributed Memory Generator 和 Block Memory Generator 两个,区别在于使用的 FPGA 资源不同,由 Distributed Memory Generator 生成的 RAM/ROM Core 占用的资源是 CLB 中的 LUT;而由 Block Memory Generator 生成的 RAM/ROM Core 占用的资源是专用的存储资源 Block Memory。

DSP 单元是专用于做高速运算的硬件资源,对乘法和累加操作做了针对性的优化,支持二进制补码操作,运算功能丰富。为了保证运算速度,DSP 单元在芯片上通常会与 Block RAM 对称布置。

时钟管理模块 CMT 是专用于产生/处理/分发时钟的硬件资源,用于将外部时钟转化为 FPGA 可用的高质量时钟,CMT 中包含 MMCM、PLL 和 Clock Buffers。

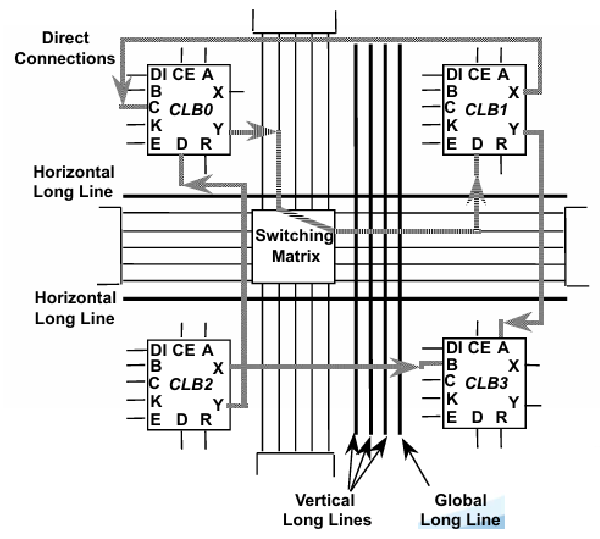

具备了上述这些各个功能模块之外,芯片内还有互联资源,用于连接各个部分的可编程硬件网络,互联资源包含可编程布线网络和可编程交换开关。内部互联结构如下

互联资源用于解决芯片内部连接,而在多颗 FPGA 硅片之间,有堆栈硅互联(SSI)技术来将多颗芯片在封装层面拼成一个超大 FPGA。