FPGA系列(0)

FPGA基本介绍

概述

FPGA 全称 Field-Programmable Gate Array(现场可编程逻辑阵列),是 PLD(Programmable Logic Device,可编程逻辑设备)的一种,通过编写硬件描述语言的代码就可以改变电路结构。FPGA 的设计初衷是减少芯片流片的成本,第一块 FPGA 于 1985 年由 Xilinx 正式推出并商用,型号为 XC2064。今天 FPGA 最多的应用仍然在于芯片的原型验证,此外 FPGA 可以将部分在 CPU 上由软件执行的工作 offload 到硬件电路上进行,因此另一个主要的用途是做硬件减速器的设计实现。

开发流程

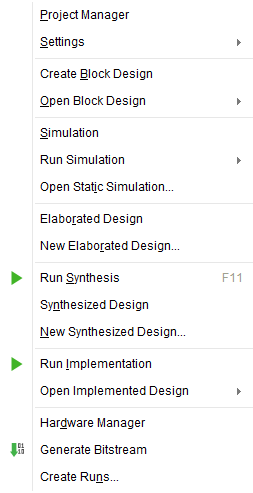

FPGA 开发流程大致可以分为以下步骤:

- 设计(Design):用 HDL 对硬件电路进行建模描述,需要定义电路功能实现、设计约束和测试用例。对于许多常用的功能,有现成的 IP 核作为轮子可以直接使用。测试用例是针对功能仿真的,由.sim 文件管理;设计约束由.xdc 文件管理。

- 功能仿真(Simulation):又称前仿真,指在计算机的仿真器上运行 Verilog 代码,在不考虑硬件电路实现和绝大部分约束的情况下,仅验证逻辑功能是否正确。

- 分析和综合(Systhesis):由 EDA 软件检查 HDL 代码是否符合综合规则,并在厂家提供的标准单元库和设计阶段中的约束下,编译出由 HDL 描述的逻辑网表并进行逻辑优化。对于 ASIC,综合将 RTL 代码映射成为目标工艺库的网表电路;而对于 FPGA,综合将 RTL 代码映射成 LUT、FF、RAM Blocks 等芯片中固定的硬件资源。注意不是所有的 HDL 语句都可以综合出相应的逻辑电路。此外,硬核 IP 已经在芯片流片时用晶体管电路实现并固化在硅片中了,不需要综合。

- 布局布线(Implementation):分配引脚并确定内部电路的连接关系,进行 layout 和 IO planning,根据设计阶段的约束文件和综合出的逻辑网表,利用厂家提供的标准元件库对门级电路进行布局,在考虑各种约束和优化的情况下,将设计中的门级网表映射到 FPGA 的物理布局上并进行物理优化。完成这一步后就将 HDL 描述的模型电路转化为标准元件库组成的数字电路,且此时的电路已经包含了时延信息。

- 时序分析(Analysis):指时序仿真,又称后仿真,用于检查信号延迟是否满足要求。时序分析有静态时序分析(STA)和动态时序分析(DTA),静态时序分析是通过计算每条路径的延迟来检查是否满足设计的时序约束;动态时序分析是模拟设计的运行,动态检查信号的传播延迟,用于验证时序边界。

- 生成比特流和板级调试(Bitstream):生成烧录到板子中的二进制文件.bit,并进行实际硬件的调试。生成比特流之前需要完成设计、综合和布局布线。比特流文件是一种专门为 FPGA 硬件配置而设计的格式,文件内容是经过优化的、以二进制形式存储的配置信息,包含了逻辑元件的映射、时序约束、硬件资源配置等所有信息,能够直接在 FPGA 上加载和执行。

##设计约束

FPGA中的设计约束包括:

- 引脚约束:又称 IO 约束、引脚绑定,将逻辑信号与物理引脚进行对应,给 FPGA 的 IO 口指定管脚号、电平标准、阻抗匹配,让工具知道 “信号接哪个脚、用什么电平、怎么匹配阻抗”。

- 时序约束:保证各信号按预期的时序顺序传输,在规定时间内到达正确的位置,主要类型包括时钟约束、输入输出延迟约束、时序路径约束等。

- 资源约束:又称面积约束,限制 FPGA 资源的使用量来适配目标 FPGA 的可用资源。

- 布局约束:用于控制设计中各逻辑单元的物理布局,确保逻辑单元被放置到 FPGA 的指定资源区域内,从而提高时序性能、减少信号延迟并优化资源使用。

Module 和 IP 核

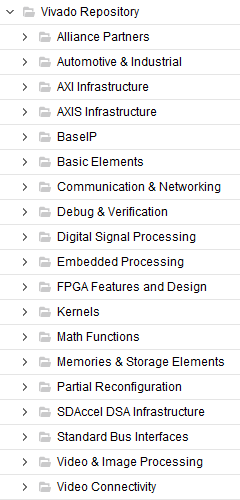

Module 一般指用户写的 RTL 代码,是纯粹的 Verilog / VHDL / SystemVerilog 模块,完全掌握源码,可综合可仿真。IP 核(Intellectual Property Core)指的是一种可复用的逻辑模块实现,可以是 HDL 描述的、可综合到 FPGA 逻辑中的软核 IP;也可以是直接固化在硅片中、不需要综合的硬核 IP。软核 IP 一般指 Xilinx 或第三方提供的与构建电路,经过了验证和优化,打包成黑盒,在工程中表现为 .xci 配置文件,存储了 IP 名称、参数配置、版本号、生成代码的路径等信息,用于告诉 Vivado 怎么生成这个 IP。有的 IP 只有 netlist(加密,看不到源码,不能直接修改逻辑),底层实现包含厂商专用的宏元件,用户不能直接手写,有的 IP 包含仿真模型和约束文件。可以自定义 IP 或添加第三方 IP。

像加法器、乘法器这样 Verilog 代码很容易实现的功能,也有相应的 IP。一行 Verilog 代码和工程级别的 IP 差距巨大,IP 的意义在于高性能的运算器,重要的是底层硬件结构。比如加法有 ripple-carry、carry lookahead、carry select、prefix adder 等实现方式;乘法有 DSP Silce、Booth、Wallace Tree 等实现方式;以及是否支持流水线,流水线级数如何配置;位宽的变化怎么处理;延迟 latency 怎么控制等。Verilog 代码的默认实现存在性能不一定够、时序不一定收敛、资源不一定最优、不确定实现的硬件资源可能是 DSP 或 LUT、跨时钟域和多周期路径无法处理、不支持 pipeline、频率上不去、不支持 ready/valid 的 backpressure 设计等一系列在实际工程中才会考虑的问题。

Xilinx 提供了功能丰富的 IP,入门阶段接触比较多的有:

- AXI 相关的:AXI Interconnect、AXI Stream FIFO、AXI DMA 等

- FPGA 基本资源相关的:Block Memory Generator、FIFO Generator、Clocking Wizard、SelectIO Interface Wizard、XADC Wizard 等

- 运算相关的:CORDIC、Divider Generator、Floating-point、FFT、DTF 等